# **AK2400**

# High integrated receiver for PMR/LMR

#### Overview

□ Operating Supply Voltage : 2.7 to 5.5V

□ Wide Operating Temperature Range : -40 to +85°C

□ Delta-Sigma Fractional-N PLL with a frequency switching function

: No glitch operation for AFC(Automatic Frequency Control) and DFM(Digital Frequency Modulation)

High linearity RF Mixer(1st) and IF Mixer(2nd)

□ IF Local frequency selectable as usage: 28.8MHz,45.9MHz,50.4MHz,57.6MHz

Frequency tripler generates IF Local signal

□ Built-in very narrow programmable bandwidth IF BPF (450kHz)

□ PLL FM detector

□ RSSI function

Noise squelch circuit

□ Built-in 12bits 1Msps SAR ADC

□ Audio output signal S/N (Wide/Narrow) : 50dB / 46dB (Typ.) \*De-emphasis + BPF

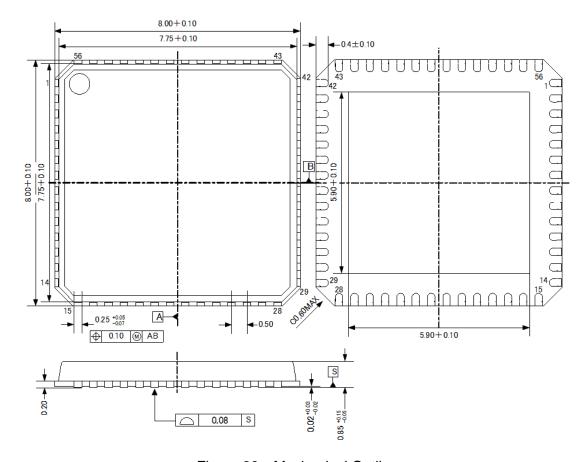

□ Compact packaging : 56pin-QFN (8 x 8 mm, 0.5 mm pitch)

### **Applications**

- Narrowband high performance professional digital wireless systems (Channel spacing for 6.25kHz,12.5kHz)

- Public safety and community wireless systems

- Marine / mobile communication systems

- □ Low power radio systems

- Monitoring and control telemeter systems

# Contents

| Overview                                                          |     |

|-------------------------------------------------------------------|-----|

| Applications ······                                               |     |

| Contents                                                          | 2   |

| Block Diagram·····                                                | 3   |

| Function                                                          | 4   |

| Pin assignment ·····                                              |     |

| Pin/Function ·····                                                |     |

| Absolute Maximum Ratings ······                                   | 7   |

| Recommended Operating Conditions                                  | 7   |

| Digital DC Characteristics                                        | 8   |

| Digital AC Timing······                                           | 9   |

| ADC AC Timing                                                     |     |

| Power-up sequence ·····                                           |     |

| System Reset ·····                                                |     |

| Analog Characteristics (PLL SYNTH)······                          | -13 |

| Analog Characteristics (1st MIXER)                                | -14 |

| Analog Characteristics (2nd IF)                                   | -15 |

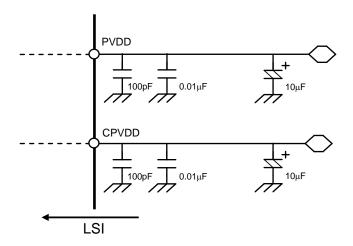

| Register Map and Function Description······                       | -21 |

| Block Diagram (PLL SYNTH) ······                                  |     |

| Lock Detect function (PLL SYNTH)                                  |     |

| Frequency Setting (PLL SYNTH)                                     | -34 |

| Frequency switching adjustment (PLL SYNTH)······                  |     |

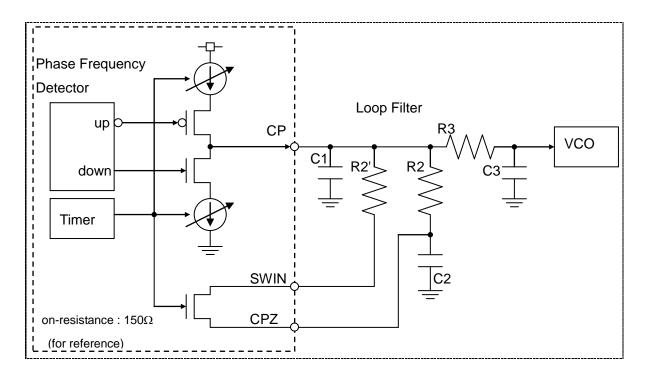

| Charge Pump and Loop Filter (PLL SYNTHE)                          |     |

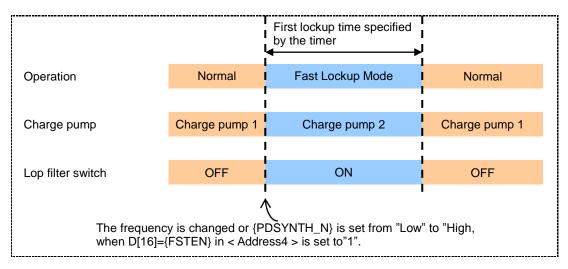

| Fast lock-up mode (PLL SYNTH)···································· |     |

| Calibration Procedure (Discriminator)                             | -38 |

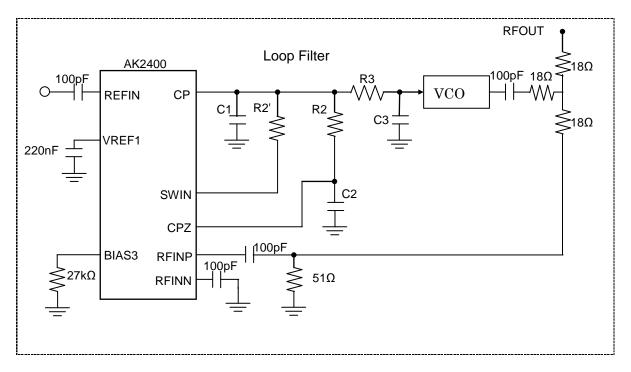

| Typical Evaluation Board Schematic (PLL SYNTH)                    |     |

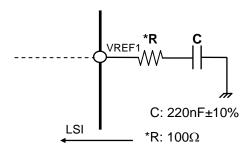

| Typical Evaluation Board Schematic (1st MIXER)                    |     |

| Typical Evaluation Board Schematic (2nd IF) ·······               |     |

| Package                                                           |     |

| Revision History ·····                                            | -50 |

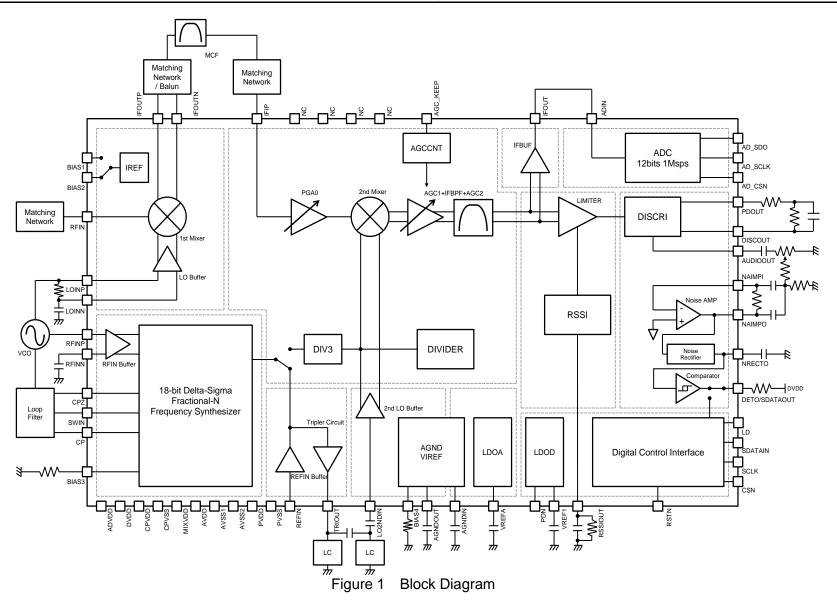

# **Block Diagram**

# **Function**

| Block           | Description                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL SYNTH       | The Delta-Sigma Fractional-N PLL (Phase Locked Loop) frequency synthesizer by the external VCO and the loop filter.                                          |

| 1stMIX          | 1st Mixer to convert the RFIN signal down to IF frequency by 1st LO signal.                                                                                  |

| PGA0+2ndMIX     | 2nd Mixer to convert the IFIP signal down to 450kHz by 2ndLO signal.                                                                                         |

| AGC+BPF         | The circuit composed of AGC and BPF, where the desired signal is amplified and spurious components included in the signal from the 2nd-mixer are eliminated. |

| IFBUF           | The circuit to output filtered signal by AGC+BPF.                                                                                                            |

| Divider         | The circuit to divide the signal from LO2NDIN pin.                                                                                                           |

| LIMITER         | The circuit to amplify the signal filtered at the AGC+BPF stage and generate rectangular wave.                                                               |

| DISCRI          | The demodulator circuit with PLL FM detector, where the audio signal is recovered.                                                                           |

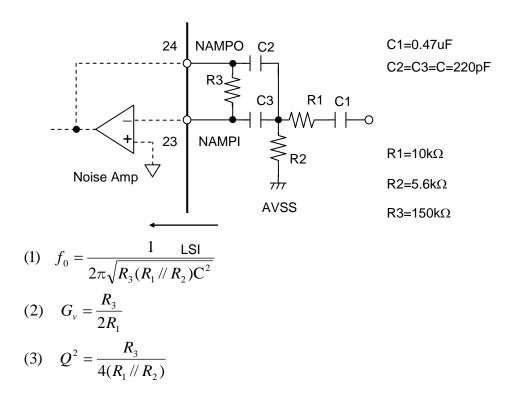

| Noise AMP       | The amplifiers to compose the Band-pass filter for noise squelch.                                                                                            |

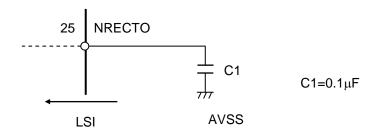

| Noise Rectifier | The rectification circuit to detect the noise level.                                                                                                         |

| Comparator      | The circuit to compare the noise level with reference voltage level.                                                                                         |

| RSSI            | The circuit to indicate the Received Signal Strength Indicator (RSSI) by generating a DC voltage corresponding to the input level from Limiter.              |

| AGND+VIREF      | The circuit to generate internal reference voltage.                                                                                                          |

| Control Logic   | The control register controls the status of internal condition by serial data that consists of 1 instruction bit, 5 address bits and 18 data bits.           |

| ADC             | 12bits 1MSPS A/D converter.                                                                                                                                  |

|                 |                                                                                                                                                              |

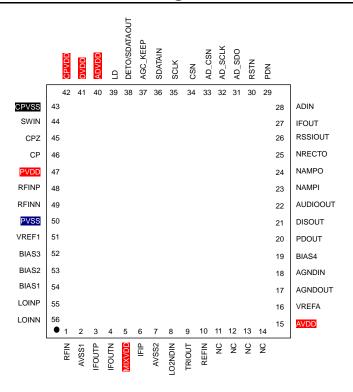

# Pin assignment

Figure 2 Pin assignment

Note) The exposed pad at the center of the backside should be connected to ground.

# Pin/Function

| No. | Name     | Туре | Conditions at power down | Function                                                                                   |

|-----|----------|------|--------------------------|--------------------------------------------------------------------------------------------|

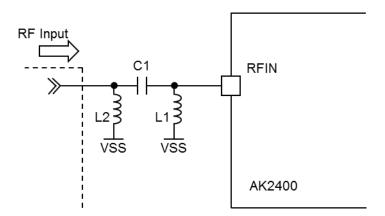

| 1   | RFIN     | Al   | -                        | RF signal input pin. Connecting a inductor between this pin and ground.                    |

| 2   | AVSS1    | PWR  | -                        | Analog VSS power supply pin                                                                |

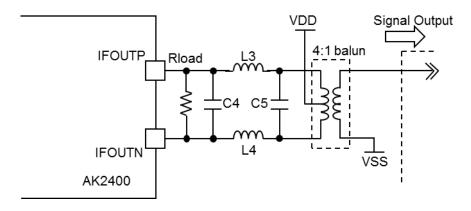

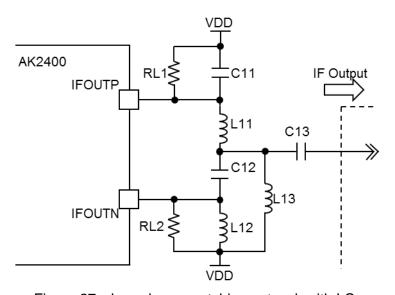

| 3   | IFOUTP   | AO   | -                        | IF Output Positive .This pin is open drain output. It needs power feeding via an inductor. |

| 4   | IFOUTN   | AO   | -                        | IF Output Negative .This pin is open drain output. It needs power feeding via an inductor. |

| 5   | MIXVDD   | PWR  | -                        | Mixer VDD power supply pin                                                                 |

| 6   | IFIP     | Al   | -                        | IF signal input pin                                                                        |

| 7   | AVSS2    | PWR  | -                        | Analog VSS power supply pin                                                                |

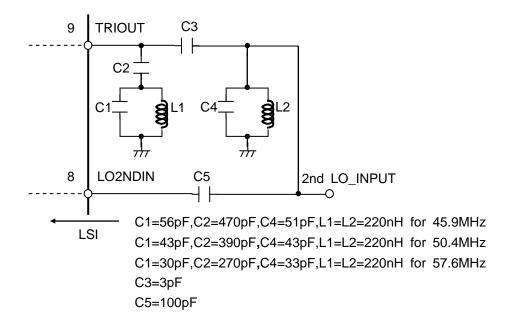

| 8   | LO2NDIN  | Al   | -                        | 2nd LO signal input pin                                                                    |

| 9   | TRIOUT   | AO   | -                        | Tripler circuit output pin                                                                 |

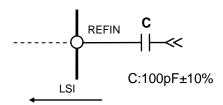

| 10  | REFIN    | Al   | -                        | Reference signal input pin                                                                 |

| 11  | NC       | -    | Hi-Z                     | This pin must be left open                                                                 |

| 12  | NC       | -    | Hi-Z                     | This pin must be left open                                                                 |

| 13  | NC       | -    | Hi-Z                     | This pin must be left open                                                                 |

| 14  | NC       | -    | Hi-Z                     | This pin must be left open                                                                 |

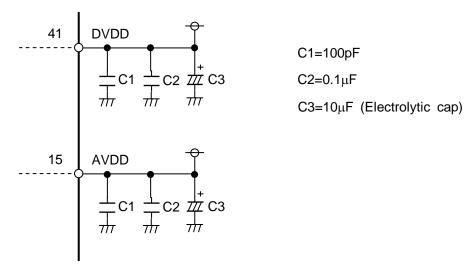

| 15  | AVDD     | PWR  | -                        | Analog VDD power supply pin                                                                |

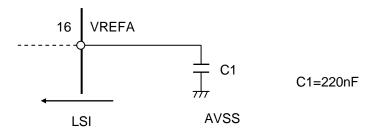

| 16  | VREFA    | AO   | -                        | LDO reference pin. Connect the capacitor to stabilize LDO reference voltage                |

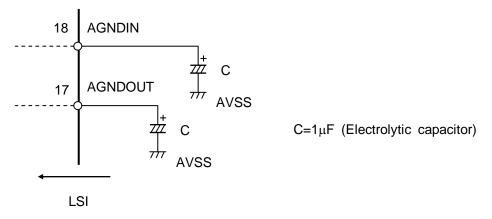

| 17  | AGNDOUT  | AO   | -                        | Analog ground output pin. Connect the capacitor to stabilize the analog ground level.      |

| 18  | AGNDIN   | Al   | -                        | Analog ground input pin. Connect the capacitor to stabilize the analog ground level.       |

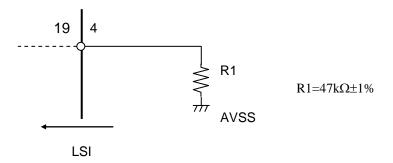

| 19  | BIAS4    | AO   | -                        | Output pin to connect bias resistor for reference voltage                                  |

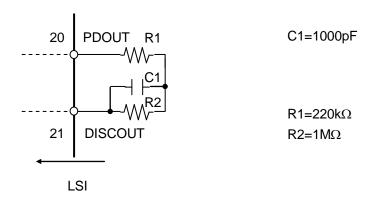

| 20  | PDOUT    | AO   | -                        | Pin1 for Discriminator Low-pass filter                                                     |

| 21  | DISCOUT  | AO   | -                        | Pin2 for Discriminator Low-pass filter                                                     |

| 22  | AUDIOOUT | AO   | -                        | Demodulated audio signal output pin                                                        |

| 23  | NAMPI    | Al   | -                        | Input pin for noise squelch amplifier                                                      |

| 24  | NAMPO    | AO   | -                        | Output pin for noise squelch amplifier                                                     |

| 25  | NRECTO   | AO   | -                        | Output pin for the rectification circuit                                                   |

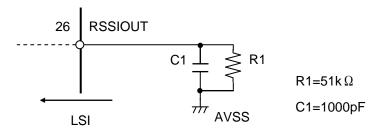

| 26  | RSSIOUT  | AO   | -                        | Output pin to connect capacitor for Received Signal Strength Indicator(RSSI)               |

| 27  | IFOUT    | AO   | -                        | Output pin for IFBUF                                                                       |

| 28  | ADIN     | Al   | -                        | Input pin for A/D converter                                                                |

| 29  | PDN      | DI   | Hi-Z                     | Power down pin for LDO                                                                     |

| 30  | RSTN     | DI   | Hi-Z                     | Hardware reset pin                                                                         |

| 31  | AD_SDO   | DO   | -                        | A/D Converter data output pin for serial data                                              |

| 32  | AD_SCLK  | DI   | Hi-Z                     | A/D Converter clock input pin for serial data                                              |

| 33  | AD_CSN   | DI   | Hi-Z                     | A/D Converter chip select input pin for serial data                                        |

| 34  | CSN      | DI   | Hi-Z                     | Chip select input pin for serial data                                                      |

| 35 | SCLK               | DI  | Hi-Z    | Clock input pin for serial data                                             |

|----|--------------------|-----|---------|-----------------------------------------------------------------------------|

| 36 | SDATAIN            | DI  | Hi-Z    | Data input pin for serial data                                              |

| 37 | AGC_KEEP           | DI  | Hi-Z    | Input pin for AGC_KEEP function                                             |

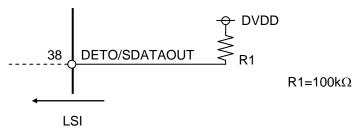

| 38 | DETO /<br>SDATAOUT | DO  | Hi-Z    | Signal detect output pin/ Data output pin for serial data                   |

| 39 | LD                 | DO  | Low     | Lock detect output pin for PLL                                              |

| 40 | ADVDD              | PWR | -       | AD VDD power supply pin                                                     |

| 41 | DVDD               | PWR | -       | Digital VDD power supply pin                                                |

| 42 | CPVDD              | PWR | -       | Charge pump VDD power supply pin                                            |

| 43 | CPVSS              | PWR | -       | Charge pump VSS power supply pin                                            |

| 44 | SWIN               | Al  | Note1,2 | Connect to resistance pin for fast lock up                                  |

| 45 | CPZ                | Al  | Note1,2 | Connect to the loop filter capacitor                                        |

| 46 | СР                 | AO  | Hi-Z    | Charge pump output pin                                                      |

| 47 | PVDD               | PWR | -       | PLL VDD power supply pin                                                    |

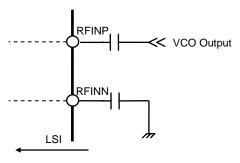

| 48 | RFINP              | Al  | -       | Prescaler input positive                                                    |

| 49 | RFINN              | Al  | -       | Prescaler input negative                                                    |

| 50 | PVSS               | PWR | -       | PLL VSS power supply pin                                                    |

| 51 | VREF1              | АО  | -       | LDO reference pin. Connect the capacitor to stabilize LDO reference voltage |

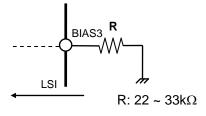

| 52 | BIAS3              | АО  | -       | Resistance pin for setting charge pump output current                       |

| 53 | BIAS2              | AIO | -       | Resistance pin for current adjustment for 1st Mixer                         |

| 54 | BIAS1              | AIO | -       | Resistance pin for current adjustment for 1st Mixer                         |

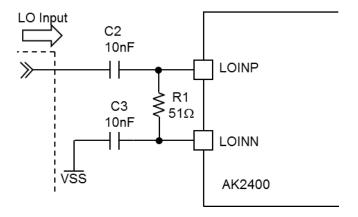

| 55 | LOINP              | Al  | -       | Lo input positive                                                           |

| 56 | LOINN              | Al  | -       | Lo input negative                                                           |

Al: Analog input pin

AO: Analog output pin

AIO: Analog I/O pin

PWR: Power supply pin

DI: Digital input pin

DO: Digital output pin

Note1) When [PDN]="0", {PDSYNTH\_N}="0", or [PDN]="1",{PDSYNTH\_N}="0", the state of the switch of loop filter selection is ON.

Note2) Power down refers to the state where [PDN]="0" after power-on.

[CPZ] pin should be connected to R2 and C2, which are intermediate nodes, even if the Fast Lockup feature is not used. For the output destination from [CPZ] pin, see "Charge Pump and Loop Filter" on page 36.

# **Absolute Maximum Ratings**

| Parameter                               | Symbol           | Min. | Max.                                | Unit | Remarks |

|-----------------------------------------|------------------|------|-------------------------------------|------|---------|

|                                         | VDD1             | -0.3 | 6.5                                 | V    | Note 1  |

| Supply Voltage                          | CPVDD            | -0.3 | 6.5                                 | V    |         |

| Supply Voltage                          | MIXVDD           | -0.3 | 5.5                                 | V    |         |

|                                         | DVDD             | -0.3 | 6.5                                 | V    |         |

| Ground level                            | VSS              | 0    | 0                                   | V    |         |

| Analog Input Voltage                    | V <sub>AIN</sub> | -0.3 | VDD1+0.3<br>CPVDD+0.3<br>MIXVDD+0.3 | V    | Note 1  |

| Digital Input Voltage                   | V <sub>DIN</sub> | -0.3 | DVDD+0.3                            | V    |         |

| Input Current (Except power supply pin) | I <sub>IN</sub>  | -10  | +10                                 | mA   |         |

| RF Input Power                          | RFPOW            |      | 12                                  | dBm  |         |

| LO Input Power                          | LOPOW            |      | 12                                  | dBm  |         |

| Storage Temperature                     | T <sub>stg</sub> | -55  | 125                                 | °C   |         |

Note 1 VDD1 is applied to PVDD, AVDD, ADVDD pins Note 2 All voltages are relative to the VSS pin.

# **Recommended Operating Conditions**

| Parameter                | Symbol | Conditions        | Min. | Тур.     | Max. | Unit |

|--------------------------|--------|-------------------|------|----------|------|------|

| Operating Temperature    | Ta     |                   | -40  |          | 85   | °C   |

|                          | VDD1   | PVDD, AVDD, ADVDD | DVDD | 3.0      | 5.5  | V    |

| Power Supply voltage     | CPVDD  |                   | VDD1 | 5.0      | 5.5  | V    |

| Tower Supply Voltage     | MIXVDD |                   | VDD1 | 5.0      | 5.5  | V    |

|                          | DVDD   |                   | 2.7  | 3.0      | 5.5  | V    |

| Analog Reference Voltage | AGND   | AGNDOUT           |      | 1/2VREFA |      | V    |

Note ) All voltages are relative to the VSS pin.

Note 3 Exceeding these maximum ratings may result in damage to the AK2400. Normal operation is not guaranteed at these extremes.

# Digital DC Characteristics

| Parameter                 | Symbol          | Conditions                                                                              | Min.     | Тур. | Max.    | Unit |

|---------------------------|-----------------|-----------------------------------------------------------------------------------------|----------|------|---------|------|

| High level input voltage  | V <sub>IH</sub> | RSTN, SCLK, SDATAIN,<br>CSN, PDN, AD_CSN,<br>AD_SCLK,, AGC_KEEP                         | 0.8DVDD  |      |         | V    |

| Low level input voltage   | V <sub>IL</sub> | RSTN, SCLK, SDATAIN,<br>CSN, PDN, AD_CSN<br>AD_SCLK, AGC_KEEP                           |          |      | 0.2DVDD | V    |

| High level input current  | I <sub>IH</sub> | V <sub>IH</sub> =DVDD<br>RSTN, SCLK, SDATAIN,<br>CSN, PDN, AD_CSN,<br>AD_SCLK, AGC_KEEP |          |      | 10      | uA   |

| Low level input current   | I <sub>IL</sub> | V <sub>IL</sub> =0V<br>RSTN, SCLK, SDATAIN,<br>CSN, PDN, AD_CSN,<br>AD_SCLK, AGC_KEEP   | -10      |      |         | uA   |

| High level output voltage | V <sub>OH</sub> | I <sub>OH</sub> =+0.2mA<br>LD, AD_SDO,<br>DETO/SDATAOUT                                 | DVDD-0.4 |      | DVDD    | V    |

| Low level output voltage  | V <sub>OL</sub> | I <sub>OL</sub> =-0.4mA<br>LD, AD_SDO,<br>DETO/SDATAOUT                                 | 0.0      |      | 0.4     | V    |

# **Digital AC Timing**

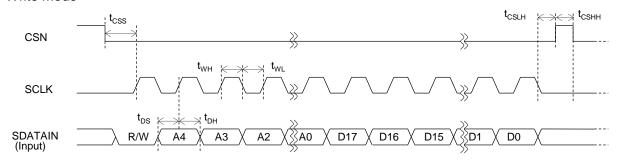

#### 1) Serial Interface Timing

AK2400 is connected to a CPU by three-wired interface through CSN, SCLK, SDATAIN and SDATAOUT pins, which can make reading and writing data for control registers.

Serial data named SDATAIN is consist of 1-bit read and write instruction(R/W), 5-bit address (A4 to A0) and 18-bit data(D17 to D0) in one frame.

#### Write mode

#### Read mode

Figure 3 Serial Interface Timing

R/W : Instruction bit controls to write data to AK2400 or read back from it.

When set to low, AK2400 is in write mode. When set to high, AK2400 is in read mode.

A4 to A0 : Register address to be accessed. D17 to D0: Write or read date to be accessed.

- <1> CSN(Chip select) is normally selected high for disable. When CSN is set to low, serial interface becomes active.

- <2> In write mode, instruction, address and data input from SDATAIN pin are synchronized and latched with the rising edge of 24 iterations of SCLK clock. Set to low between address A0 and data D17.Input data is fixed synchronized with the rising edge of 24th clock. Note that if CSN become "H" before 24th clock, setting data becomes invalid. During the period when CSN is set to "L", consecutive writing is available.

- <3> In read mode, instruction and address are synchronized and latched with the rising edge of 6 iterations of SCLK clock. And the register data are output from SDATAIN pin synchronized with the falling edge of 18 iterations of SCLK clock. CSN to "H" once reading is completed because consecutive reading is not valid. Also, in read mode DETO/SDATAOUT pin should be set to SDATAOUT by {SDATAOUT\_OE}="1".

| Parameter                       | Symbol            | Conditions | Min. | Тур. | Max. | Unit |

|---------------------------------|-------------------|------------|------|------|------|------|

| CSN setup time                  | t <sub>CSS</sub>  |            | 40   |      |      | ns   |

| SDATAIN setup time              | t <sub>DS</sub>   |            | 20   |      |      | ns   |

| SDATAIN hold time               | t <sub>DH</sub>   |            | 20   |      |      | ns   |

| SCLK high time                  | $t_{WH}$          |            | 40   |      |      | ns   |

| SCLK low time                   | $t_WL$            |            | 40   |      |      | ns   |

| CSN low hold time               | t <sub>CSLH</sub> |            | 20   |      |      | ns   |

| CSN high hold time              | t <sub>CSHH</sub> |            | 40   |      |      | ns   |

| SCLK to SDATA output delay time | t <sub>DD</sub>   | 20pF load  |      |      | 40   | ns   |

Note) Digital input and output timing is relative to 0.5DVDD of rising signal and falling signal.

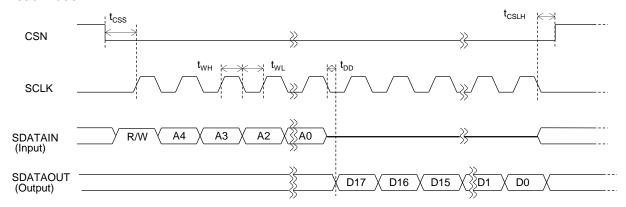

# **ADC AC Timing**

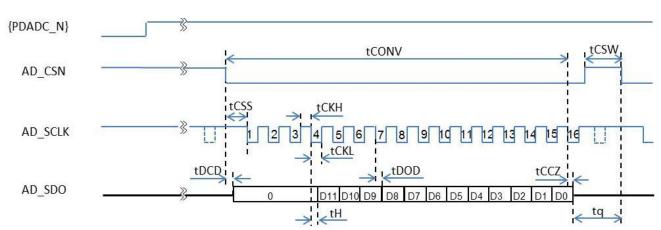

At first, set {PDADC\_N}="1" to operate the A/D Converter. A/D conversion cycle is started by the falling edge of AD\_CSN. AD\_SDO outputs "0" synchronized with the falling edge of AD\_CSN. AD\_SDO outputs "0" until the third falling edge of AD\_SCLK. From the fourth falling edge, the results of 12 bits A/D conversion are output with MSB first during the 16th edge. A/D conversion cycle is ended on the 16th falling edge, AD\_SDO becomes Hi-Z. After the 16th edge, set AD\_CSN ="1". Since A/D converter becomes acquisition phase after the 16th falling edge of AD\_SCLK, AD\_CSN pin must keep "1" during the end of "tq" time after AD\_SDO became Hi-Z. It is possible to get the available conversion results from the next cycle, since the first A/D conversion result is the dummy cycle (unavailable result).

D11 to D0: A/D converted data

Figure 4 ADC Timing

| Parameter                                                                       | Symbol  | Conditions | Min.            | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------|---------|------------|-----------------|------|------|------|

| AD_SCLK frequency                                                               | fADSCLK |            |                 |      | 20   | MHz  |

| Minimum quiet time required between bus relinquish and start of next conversion | Tq      |            | 40              |      |      | ns   |

| AD_CSN Falling to First SCLK Falling time                                       | tCSS    |            | 10              |      |      | ns   |

| AD_CSN edge to AD_SDO Tri-State Disabled                                        | tDCD    |            |                 |      | 25   | ns   |

| AD_SCLK Falling to AD_SDO Output Delay time                                     | tDOD    | 15pF load  |                 |      | 25   | ns   |

| AD_SCLK High Pulse Width                                                        | tCKH    |            | 0.4×tA<br>DSCLK |      |      | ns   |

| AD_SCLK Low Pulse Width                                                         | tCKL    |            | 0.4×tA<br>DSCLK |      |      | ns   |

| 16th AD_SCLK Falling to AD_SDO Hi-Z State Delay time                            | tCCZ    |            |                 |      | 25   | ns   |

| Minimum AD_CSN Pulse Width                                                      | tCSW    |            | 25              |      |      | ns   |

Note) Digital input and output timing is relative to 0.5DVDD of rising signal and falling signal.

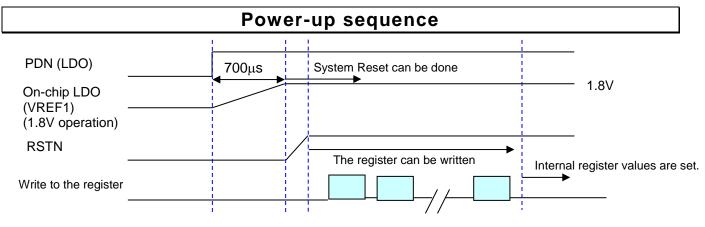

Figure 5 power-up sequence

Note) Power-up sequence assumes VDD ON.

After PDN is set to "High", registers remain undefined. In order to initialize them, RSTN is set to "High"

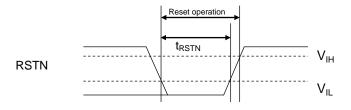

### System Reset

| Parameter                         | Symbol            | Conditions       | Min. | Тур. | Max. | Unit | Remarks |

|-----------------------------------|-------------------|------------------|------|------|------|------|---------|

| Hardware reset signal input width | t <sub>RSTN</sub> | RSTN pin         | 1    |      |      | μS   | Note 1) |

| Software reset                    |                   | SRST<br>register |      |      |      |      | Note 2) |

Note1) After power-on, be sure to perform a hardware reset operation (register initialization). The system is reset by a Low input of 1us (min.) and enters the normal operation state.

Figure 6 System Reset

During the reset operation, SCLK, SDATAIN and CSN pin should be keep to Low or High. Ex) SCLK:Low, SDATAIN:Low, CSN:High

Note2) When data 0x09:10101010 is written to the SRST[7:0] register, software reset is performed. This setting initializes the registers and the operation mode is set to mode 2 (Standby 2). After software reset is completed, this register comes to "0".

# **Analog Characteristics (PLL SYNTH)**

Unless otherwise noted VDD=2.7 to 5.5V, Ta=-40°C to 85°C.

| Parameter Parameter              | Min                | Тур.         | Max           | Unit    | Remarks                      |  |  |  |  |  |  |

|----------------------------------|--------------------|--------------|---------------|---------|------------------------------|--|--|--|--|--|--|

|                                  | RF Characteristics |              |               |         |                              |  |  |  |  |  |  |

| Input Sensitivity                | -10                |              | 5             | dBm     |                              |  |  |  |  |  |  |

| Input Frequency                  | 40                 |              | 500           | MHz     | Prescaler 4/5                |  |  |  |  |  |  |

| input i requeitey                | 40                 |              | 1000          | MHz     | Prescaler 8/9,16/17          |  |  |  |  |  |  |

| REFIN Characteristics            |                    |              |               |         |                              |  |  |  |  |  |  |

| Input Sensitivity                | 0.4                | 45.0         | 2             | Vpp     |                              |  |  |  |  |  |  |

| Input Frequency                  |                    | 15.3<br>16.8 |               | MHz     | Note 1)                      |  |  |  |  |  |  |

| input Frequency                  |                    | 19.2         |               | IVITIZ  | Note 1)                      |  |  |  |  |  |  |

|                                  |                    | _            | ency Detector | ſ       |                              |  |  |  |  |  |  |

| Phase Detector                   | •                  |              |               |         |                              |  |  |  |  |  |  |

| Frequency                        |                    |              |               | IVII IZ |                              |  |  |  |  |  |  |

|                                  |                    | Charg        | e Pump        | T       |                              |  |  |  |  |  |  |

| Charge Pump 1                    |                    | 168.9        |               | μA      | BIAS3=27k $\Omega$ , Note 2) |  |  |  |  |  |  |

| Maximum Value Charge Pump 1      |                    |              |               |         | ,                            |  |  |  |  |  |  |

| Minimum Value                    |                    | 21.1         |               | μA      | BIAS3=27k $\Omega$ , Note 2) |  |  |  |  |  |  |

| Charge Pump 2                    |                    | 2.22         |               |         |                              |  |  |  |  |  |  |

| Maximum Value                    |                    | 2.32         |               | mA      | BIAS3=27k $\Omega$ , Note 3) |  |  |  |  |  |  |

| Charge Pump 2                    |                    | 0.84         |               | mA      | BIAS3=27kΩ, Note 3)          |  |  |  |  |  |  |

| Minimum Value                    |                    | 0.04         |               | ША      | •                            |  |  |  |  |  |  |

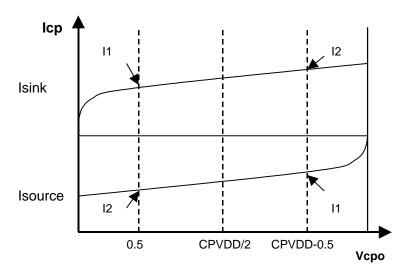

| Icp TRI-STATE                    |                    | 1            |               | nA      | 0.6≦Vcpo≦CPVDD-0.7           |  |  |  |  |  |  |

| Leak Current                     |                    |              |               |         | (Vcpo:CP pin voltage)        |  |  |  |  |  |  |

| Mismatch between Source and Sink |                    |              | 10            | %       | Vcpo= CPVDD/2                |  |  |  |  |  |  |

| Currents Note 4)                 |                    |              | 10            | 70      | Ta=25°C                      |  |  |  |  |  |  |

| Icp vs. Vcpo                     |                    |              |               |         | 0.5≦Vcpo≦CPVDD-0.5           |  |  |  |  |  |  |

| Note 5)                          |                    |              | 15            | %       | Ta=25°C                      |  |  |  |  |  |  |

|                                  |                    | Current C    | onsumption    |         |                              |  |  |  |  |  |  |

| IDD_SYN1                         |                    |              | 10            | μA      | PDN=0                        |  |  |  |  |  |  |

| IDD_SYN2                         |                    | 2.4          | 3.6           | mA      | Note 6)                      |  |  |  |  |  |  |

| IDD_SYN3                         |                    | 0.17         |               | mA      | Note 7)                      |  |  |  |  |  |  |

- Note 1) REFIN pin is input one third of the 2nd LO input frequency.

- Note 2) Charge pump 1 current is determined by the setting in {CP1[2:0]} which is described on page 22.

- Note 3) Charge pump 2 current is determined by the setting in {CP2[2:0]} which is described on page 23.

- Note 4) Mismatch between Source and Sink Currents: [(|Isink|-|Isource|)/{(|Isink|+|Isource|)/2}] × 100 [%]

- Note 5) | Icp vs. Vcpo: [{1/2x(|I1|-|I2|)}/{1/2x(|I1|+|I2|)}]x100 [%]

- Note 6) [PDN]="High", {PDSYNTH N}="High" IDD for [PVDD]

- Note 7) [PDN]="High", {PDSYNTH N}="High" IDD for [CPVDD]

IDD does not include the operation current in fast lockup mode.

- Note ) [PDN]="High", {PDSYNTH\_N}="High", the total current consumption = IDD\_SYN2+IDD\_SYN3

- Note ) In the shipment test, the exposed pad on the center of the back of the package is connected to ground.

- Note ) When 2nd LO input frequency is used 28.8MHz, set {PDTRI\_N}=0 and input the 2nd LO signal(28.8MHz) from LO2NDIN pin. Then REFIN Frequency is set 28.8MHz/3=9.6MHz.

Figure 7 Charge Pump Characteristics - Voltage vs. Current

# **Analog Characteristics (1st MIXER)**

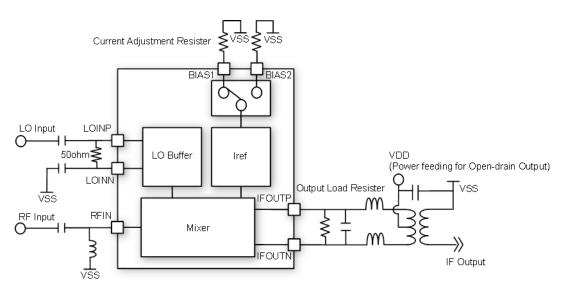

Unless otherwise noted IF output=50MHz, Lo Input Level=-10dBm to +5dBm, {FMIX\_HV}=0, {FMIX\_IP3}=0, Output Load Resistor (RLoad)=2.2k $\Omega$ , VDD=2.7 to 5.5V, Ta=-40°C to 85°C, Test circuit is shown on page 41.

Parameter Min. Max. Unit Remarks Тур. **RF Input Frequency** 10 2000 MHz Lo Input Frequency 10 2000 MHz IF output Frequency 20 100 MHz Lo Input Power -10 0 +5 dBm Current Adjustment Resistor(BIAS) 39 100 kΩ Vdd=2.7 to 5.5V  $(\{FMIX_HV\}=0)$ Current Adjustment Resistor(BIAS) Vdd=4.5 to 5.5V 18 39 kΩ  $(\{FMIX_HV\}=1)$  $IDD(BIAS=18k\Omega, \{FMIX_HV\}=1)$ 24 mΑ The total current of IDD(BIAS=47kΩ) 9 13 mΑ MIXVDD, IFOUTP, IDD({PDFSTMIX\_N}=0) 10 IFOUTN. uA RFIN=600MHz, LOIN=550MHz(0dBm), BIAS=47kΩ, Vdd=3V Conversion Gain 0.5 3 5 dB SSB Noise Figure 8.5 11 dΒ Design guarantee value IP1dB -3 dBm 1 IIP3 11 dBm RFIN=600MHz, LOIN=550MHz(0dBm), BIAS=18k $\Omega$ , {FMIX\_HV}=1,Vdd=5V Conversion Gain dB 8.5 dB SSB Noise Figure Design guarantee value IP1dB 0 dBm IIP3 16 dBm Design guarantee value RFIN=600MHz, LOIN=550MHz(0dBm), BIAS=47kΩ, Vdd=3V, {FMIX\_IP3}=1 Conversion Gain dB 10 SSB Noise Figure dB Design guarantee value IP1dB 0 dBm IIP3 14 dBm Design guarantee value IDD 7 mΑ

# **Analog Characteristics (2nd IF)**

Unless otherwise noted VDD=2.7 to 5.5V, Ta=-40°C to 85°C.

Mode 6, LO2NDIN=50.4MHz,IFIP=50.85MHz,  $\Delta f = \pm 1.5$ kHz, fmod=1kHz, AGC+BPF=F2, {AGC\_OFF}=0, {AGC\_KEEP\_SEL}=0, {AGC\_KEEP}=0, PGA0[2:0]=011. {SDATAOUT\_OE}=0. The exposure back pad of the package is connected to VSS. Test circuit is shown on page 45.

1) 2nd LO input

| Parameter       | Symbol          | Conditions | Min. | Тур.                         | Max. | Unit     | Remarks |

|-----------------|-----------------|------------|------|------------------------------|------|----------|---------|

| Parameter       | F <sub>LO</sub> | LO2NDIN    |      | 28.8<br>45.9<br>50.4<br>57.6 |      | MHz      |         |

| Local Frequency | $V_{LO}$        | LO2NDIN    | 0.2  |                              | 2.0  | $V_{PP}$ | Note    |

Note) Input from LO2NDIN pin through DC cut

#### 2) PGA0+2nd Mixer

Analog Characteristics (2nd IF) are included the circuit of IFIP input pin.

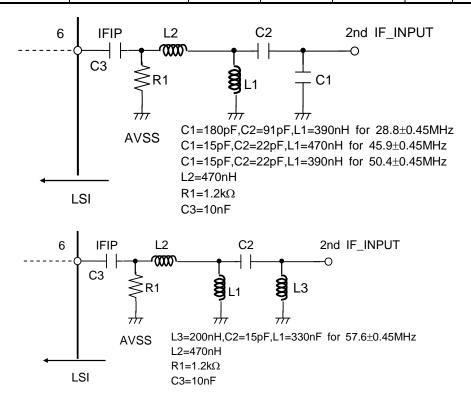

The input impedance of 2nd IF\_INPUT is  $50\Omega$  typ. (See Figure 8 for input matching network)

| Parameter       | Conditions | Min. | Тур.                     | Max. | Unit | Remarks |

|-----------------|------------|------|--------------------------|------|------|---------|

| Input Impedance |            |      | 50                       |      | Ω    |         |

| Input Frequency |            |      | F <sub>LO</sub><br>±0.45 |      | MHz  |         |

| Voltage Gain    |            |      | 48                       |      | dB   |         |

Figure 8 Test circuit of IFIP Input pin (2nd IF)

#### 3) 2nd IF RX overall characteristics

| Parameter                       | Conditions                                                                                        | Min. | Тур. | Max. | Unit  | Remarks |

|---------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|-------|---------|

| 12dB SINAD                      | Note 1)                                                                                           |      | -112 |      | dBm   |         |

| 2nd IF block                    | Mode 5 Maximum gain setting for AGC IFIP to IFOUT {IFOG[2:0]}=001                                 |      | 101  |      | dB    |         |

| Total Gain                      | Mode 5 Minimum gain setting for AGC IFIP to IFOUT {IFOG[2:0]}=001                                 |      | 49   |      | dB    |         |

| NF                              | Mode 5, BPF=F3 Maximum gain setting for AGC IFIP to IFOUT {IFOG[2:0]}=001                         |      | 8    |      | dB    |         |

| IIP3                            | Maximum gain setting for AGC IFIP=50.8635MHz&50.876MHz {IFOG[2:0]}=001                            |      | -37  |      | dBm   |         |

| IP1dB                           | Minimum gain setting for AGC<br>{IFOG[2:0]}=001                                                   |      | -40  |      | dBm   |         |

| Demodulation<br>Output          | $\Delta f=\pm 3.0 \text{kHz,fmod}=1 \text{kHz,}$<br>$\Delta GC+BPF=F1,\{DISLPF\_G[2:0]\}=101$     | 70   | 100  | 130  | mVrms |         |

| Level                           | $\Delta f=\pm 1.5$ kHz,fmod=1kHz,<br>AGC+BPF=F2,{DISLPF_G[2:0]}=001                               | 70   | 100  | 130  | mVrms |         |

| S/N Ratio                       | $\Delta$ f= $\pm$ 3.0kHz,fmod=1kHz,Vin=-47dBm AGC+BPF=F1, {DISLPF_G[2:0]}=101 Note 1)             | 42   | 50   |      | dB    |         |

| 3/N Kalio                       | $\Delta$ f= $\pm$ 1.5kHz,fmod=1kHz,Vin=-47dBm AGC+BPF=F2, {DISLPF_G[2:0]}=001 Note 1)             | 36   | 46   |      | dB    |         |

| Audio Frequency characteristics | Δf=±0.5kHz,fmod=3kHz,Vin=-47dBm<br>AGC+BPF=F3,<br>IFIP to AUDIOOUT<br>{DISLPF_G[2:0]}=001 Note 2) | -4.3 | -3.5 |      | dB    |         |

Note 1) With De-emphasis+BPF(0.3 to 3kHz)

Note 2) relative to the output level at fmod=1kHz

# 4) RSSI Characteristics

| Parameter               | Conditions                                         | Min. | Тур. | Max. | Unit | Remarks |

|-------------------------|----------------------------------------------------|------|------|------|------|---------|

| DOOL and and another an | IFIP→RSSIOUT,<br>{AGC_OFF}=0<br>IFIP=-115dBm input |      | 0.6  |      | V    |         |

| RSSI output voltage     | IFIP→RSSIOUT,<br>{AGC_OFF}=0<br>IFIP=-45dBm input  |      | 2.2  |      | V    |         |

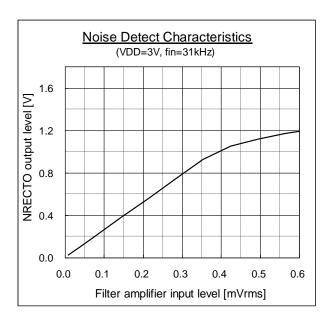

5) Noise Squelch Characteristics

| Parameter                | Conditions                               | Min. | Тур. | Max. | Unit | Remarks |

|--------------------------|------------------------------------------|------|------|------|------|---------|

| Noise Detection<br>Level | NRECTO→DETO<br>Detect High               |      | 0.5  | 0.7  | V    |         |

|                          | NRECTO→DETO<br>Detect Low                | 0.3  | 0.4  |      | V    |         |

| Noise Detection          | NAMPI→NRECTO<br>Input : 31kHz, 0.1mVrms  |      | 0.3  |      | V    |         |

| Characteristics          | NAMPI→NRECTO<br>Input : 31kHz, 0.25mVrms |      | 0.65 |      | V    |         |

# 6) AGC+BPF

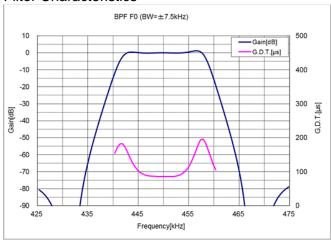

6.1) F0 (E type)

| Parameter                        | Conditions      | Min. | Тур. | Max. | Unit | Remarks |

|----------------------------------|-----------------|------|------|------|------|---------|

|                                  | 435kHz          |      |      | -50  | dB   |         |

| Attenuation Characteristics      | 442.5kHz        | -6   |      |      | dB   |         |

| (relative to the gain at 450kHz) | 457.5kHz        | -6   |      |      | dB   |         |

|                                  | 465kHz          |      |      | -50  | dB   |         |

| Gain ripple                      | Within 450±5kHz |      |      | 3    | dB   |         |

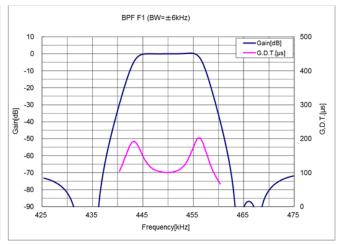

6.2) F1 (F type)

| Parameter                        | Conditions      | Min. | Тур. | Max. | Unit | Remarks |

|----------------------------------|-----------------|------|------|------|------|---------|

|                                  | 437.5kHz        |      |      | -50  | dB   |         |

| Attenuation Characteristics      | 444kHz          | -6   |      |      | dB   |         |

| (relative to the gain at 450kHz) | 456kHz          | -6   |      |      | dB   |         |

|                                  | 462.5kHz        |      |      | -50  | dB   |         |

| Gain ripple                      | Within 450±4kHz |      |      | 3    | dB   |         |

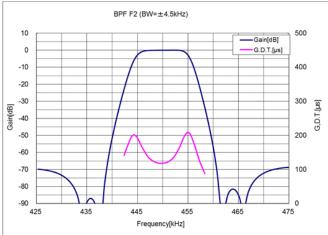

6.3) F2 (G type)

| Parameter                        | Conditions      | Min. | Тур. | Max. | Unit | Remarks |

|----------------------------------|-----------------|------|------|------|------|---------|

|                                  | 439kHz          |      |      | -50  | dB   |         |

| Attenuation Characteristics      | 445.5kHz        | -6   |      |      | dB   |         |

| (relative to the gain at 450kHz) | 454.5kHz        | -6   |      |      | dB   |         |

|                                  | 461kHz          |      |      | -50  | dB   |         |

| Gain ripple                      | Within 450±3kHz |      |      | 3    | dB   |         |

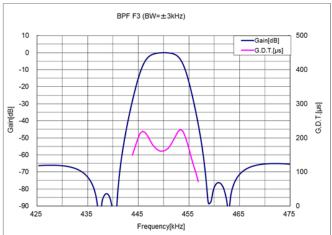

6.4) F3 (H type)

| Parameter                        | Conditions      | Min. | Тур. | Max. | Unit | Remarks |

|----------------------------------|-----------------|------|------|------|------|---------|

|                                  | 441kHz          |      |      | -50  | dB   |         |

| Attenuation Characteristics      | 447kHz          | -6   |      |      | dB   |         |

| (relative to the gain at 450kHz) | 453kHz          | -6   |      |      | dB   |         |

|                                  | 459kHz          |      |      | -50  | dB   |         |

| Gain ripple                      | Within 450±2kHz |      |      | 2    | dB   |         |

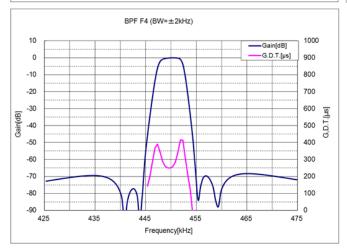

6.5) F4 (J type)

| Parameter                        | Conditions        | Min. | Тур. | Max. | Unit | Remarks |

|----------------------------------|-------------------|------|------|------|------|---------|

|                                  | 443kHz            |      |      | -50  | dB   |         |

| Attenuation Characteristics      | 448kHz            | -8   |      |      | dB   |         |

| (relative to the gain at 450kHz) | 452kHz            | -8   |      |      | dB   |         |

|                                  | 457kHz            |      |      | -50  | dB   |         |

| Gain ripple                      | Within 450±1.5kHz |      |      | 3.5  | dB   |         |

#### Filter Characteristics

7) IFBUF Characteristics

| Parameter     | Conditions                                                                | Min. | Тур. | Max. | Unit | Rema<br>rks |

|---------------|---------------------------------------------------------------------------|------|------|------|------|-------------|

| Settling time | IFBUF to IFOUT, IFBUF=0.32Vpp/step C <sub>L2</sub> =21pF, {IFOG[2:0]}=001 |      | 100  |      | ns   |             |

Note ) Convergence time within 1% when 0.32Vpp step signal input to IFBUF pin

8) Current Consumption

| Parameter   | Symbol | Conditions                                         | Min. | Тур. | Max. | Unit |

|-------------|--------|----------------------------------------------------|------|------|------|------|

|             | IDD0   | Mode0<br>Power down                                |      |      | 0.01 | mA   |

|             | IDD1   | Mode1<br>(Prohibited)                              |      |      | -    | mA   |

| ID          | IDD2   | Mode2<br>Standby(Initial value)                    |      | 0.1  | 0.15 | mA   |

| Current     | IDD3   | Mode3                                              |      | 1    | 1.5  | mA   |

| Consumption | IDD4   | Mode4, Digital Mode 1 with no signal input         |      | 7    | 11   | mA   |

|             | IDD5   | Mode5 Digital Modo 2 with no signal input. Note 2) |      | 7.5  | 12   | mA   |

|             | IDD6   | Mode6 Analog Mode with no signal input Note 2)     |      | 7.5  | 12   | mA   |

|             | IDD7   | Mode7 Full Power On with no signal nput Note 2)    |      | 8.5  | 13   | mA   |

Note 1) Current Consumption is AVDD pin.

Note 2) Tripler circuit : ON Note 3) Do not use Mode1.

Analog Characteristics (ADC)

Unless otherwise noted VDD=2.7 to 5.5V, Ta=-40°C to 85°C. fs=1MHz , ADVDD = 3.0V, AD\_SCLK=20MHz

| Parameter                             | Min. | Тур. | Max.  | Unit |

|---------------------------------------|------|------|-------|------|

| Resolution                            |      | 12   |       | Bits |

| No Missing Codes Note 2)              | 11   |      |       | Bits |

| Integral Nonlinearity (INL) Error     |      | ±2   |       | LSB  |

| Differential Nonlinearity (DNL) Error |      | ±1   |       | LSB  |

| Input Voltage Range                   | 0    |      | ADVDD | V    |

| ADVDD Power Current                   |      | 2    | 3.8   | mA   |

Note 1) The above is the characteristics of only A/D converter block.

Note 2) Design guarantee value

#### Register Map and Function Description Name D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Address NUM 0x01 NUM [17] [16] [15] [14] [13] [12] [11] [10] [9] [8] [7] [6] [5] [4] [3] [2] [1] [0] Initial Value 0 0 0 0 0 0 0 0 0 0 0 0 0 0 CP1 CP1 CP1 INT 0x02 INT [2] [14] [13] [12] [10] [9] [7] [4] [2] [1] [0] [11] [8] [6] [5] [3] [1] [0] Initial value 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 СР DCKSEL LDCKSEL[ PRE PRE R1 R1 R1 R1 R1 R1 R1 0x03 0 INTE DITH LD DIV POLA [7] [6] [5] [4] [3] [2] [1] [0] Initial value 0 1 0 0 FAST CP2 CP2 FAST FAST FAST FAST FAST CP2 FAST FAST **FAST** FAST FAST FAST FAST FAST 0x04 0 CP FAST ΕN [2] [1] [0] [12] [11] [10] [9] [8] [7] [6] [5] [4] [3] [2] [1] [0] Initial value 0 0 0 0 0 0 0 0 0 VTSEL VTSEL 0x05 0 0 0 0 0 0 0 0 0 0 0 NSQ [1] [0] 0 Initial value 0 0 0 0 0 0 0 0 0 0 0 0 0 0 OFST OFST OFST **OFST OFST** OFST **OFST OFST OFST OFST OFST OFST** OFST OFST **OFST OFST OFST OFST** 0x06 **OFFSET** [17] [16] [15] [14] [4] [13] [12] [11] [10] [9] [8] [7] [6] [5] [3] [2] [1] [0] Initial value 0 0 AGC\_KEE AGCLVL AGCLVL AGCLVL AGCLVL AGC\_FAS BPF BW BPF BW BPF BW LOFREQ LOFREQ **AGCLVL** AGCLVL. AGC AGC\_ AGC1 AGC\_ CAL 0x07 TIME[1] TIME[0] STEP [2] OFF [0] [1] [0] **IFBPF** H[2] H[1] H[0] L[2] L[1] L[0] Initial value 0 1 0 0 0 1 PGA0 L PGA2 G PGA2 G PGA2\_G PGA2\_G PGA1\_G PGA1\_G PGA1\_G PGA2\_G PGA1\_G PGA1\_G PGA1\_G PGA0\_ PGA0 PGA0 **IFOG** IFOG **IFOG** 0x08 [5] [2] [2] [1] [2] [0] **PGA** 0 0 0 0 0 0 0 0 0 0 1 0 1 1 0 0 1 Initial value 0 SRST SRST SRST SRST SRST SRST SRST SRST 0x09 0 0 0 0 0 0 0 0 0 [7] [6] [4] [3] [2] [1] [0] **SRST** Initial value AGC KEE SDATAOL DISLPF G DISLPF G DISLPF\_G PDSYNTH **PDFSTMI** BSSEL F PDADC N FMIX\_IP3 0x0A **RSSIMD** FMIX HV PDTRI N BS[2] BS[1] BS[0] 0 P SEL T OE [0] MIX PD 0 0 0 Initial value 0 0 0 0 0 0 0 0 R\_AGC1 R\_AGC1 R\_AGC1 R\_AGC1 R\_AGC1 \_AGC1 R\_AGC2 R\_AGC2 R\_AGC2 R\_AGC2 \_AGC2 0x0B G[4] G[3] G[0] G[4] G[3] G[2] G[1] G[0] PD AGCG Initial value

Note1) Writing into address 0x01 is enabled when writing into address 0x02 is performed. Be sure to write into address 0x01 first and then address 0x02.

Note2) The initial register values are not defined. Therefore, even after [PDN] is set to "High", each bit initial value remains undefined. In order to set all register values, it is required to write the data in all addresses of the register.

Note3) Do not access the data except specified address 0x0c to 0x1F.

#### Address 0x01

Note) Writing into address 0x01 is enabled when writing into address 0x02 is performed.

#### **NUM[17:0]**: Set the numerator in 2's complementary representation.

#### Address 0x02

#### CP1[2:0]: Sets the current value for the charge pump in normal operation (Charge Pump 1).

Charge Pump 1 current is determined by the following formula: CP1\_min = 0.57 / Resistance connected to the [BIAS] pin

Charge Pump 1 current = CP1  $min \times (CP1 \text{ setting } + 1)$

|          | Charge Pump 1 current [uA] |       |       |  |  |  |  |  |

|----------|----------------------------|-------|-------|--|--|--|--|--|

| CP1[2:0] | 22kΩ                       | 27 kΩ | 33 kΩ |  |  |  |  |  |

| 000      | 25.9                       | 21.1  | 17.3  |  |  |  |  |  |

| 001      | 51.8                       | 42.2  | 34.5  |  |  |  |  |  |

| 010      | 77.7                       | 63.3  | 51.8  |  |  |  |  |  |

| 011      | 103.6                      | 84.4  | 69.1  |  |  |  |  |  |

| 100      | 129.5                      | 100.6 | 86.4  |  |  |  |  |  |

| 101      | 155.5                      | 126.7 | 103.6 |  |  |  |  |  |

| 110      | 181.4                      | 147.8 | 120.9 |  |  |  |  |  |

| 111      | 207.3                      | 168.9 | 138.2 |  |  |  |  |  |

#### INT[14:0]: Sets the integer.

When {PRE[1:0]} ="00", P = 4 is selected and then an integer from 48 to 8191 can be set.

When {PRE[1:0]} ="01", P = 8 is selected and then an integer from 116 to 16383 can be set.

When {PRE[1:0]} ="10" or "11", P = 16 is selected and then an integer from 348 to 32767 can be set.

#### Address 0x03

#### INTE: INTEGER mode

0 : Disable

1 : Enable (The delta-sigma circuit is integer mode operation.

Don't use DFM operation.)

### CPHIZ: Selects normal or TRI-STATE for the CP1/CP2 output.

0 : Charge pumps are activated. (Use this setting for normal operation.)

1: TRI-STATE (The charge pump output is put in the high-impedance (Hi-Z) state.)

#### **DITH**: Selects dithering ON or OFF for a delta-sigma circuit.

0 : DITH OFF (Low Noise mode)

1 : DITH ON (Low Spurious mode)

When OFFSET register is used, set DITH=0(OFF).

### LDCKSEL[1:0]: Sets phase error values for lock detect.

When DITH="1":

VCO frequency > [REFIN] pin input frequency / [LDCKSEL[1:0] setting + 1]  $\times$  7 When DITH="0" :

VCO frequency > [REFIN] pin input frequency / [LDCKSEL[1:0] setting + 1] x 4

"00": 1 cycle of the REFIN clock (This cannot be used for the reference dividing ratio ≤ 3.)

"01": 2 cycle of the REFIN clock (This cannot be used for the reference dividing ratio ≤ 5.)

"10": 3 cycle of the REFIN clock (This cannot be used for the reference dividing ratio ≤ 6.)

"11": 1 cycle of the REFIN clock (This must be used for the reference dividing ratio = 3)

#### LD: Selects analog or digital for the lock detect.

0 : Digital Lock Detect

1 : Analog Lock Detect

#### CPPOLA: Selects positive or negative output polarity for Charge Pump1 and Charge Pump2.

0 : Positive 1 : Negative

#### PRE[1:0]: Selects a dividing ratio for the prescaler.

"00": P=4

"01": P=8

"10": P=16

"11": P=16

#### R1[7:0]: Sets a dividing ratio for the reference clock.

This can be set in the range from 3 (3 divisions) to 255 (255 divisions). 0 to 2 cannot be set.

#### Address 0x04

#### FASTEN: Enables or disables the Fast Lockup mode. FAST

0: The switchover settings specified in CP2[2:0] and FAST[12:0] are disabled.

1: The switchover settings specified in CP2[2:0] and FAST[12:0] are enabled.

### CP2[2:0]: Sets the current value for the charge pump for the Fast Lockup mode

(Charge Pump 2).

Charge Pump 2 current is determined by the following formula:

CP2 min = 0.57 / Resistance connected to the [BIAS] pin

Charge Pump 2 current =  $CP2_{min} \times (CP2 \text{ setting } + 4) \text{ [mA]}$

|          | Charge Pump 2 current [mA] |       |       |  |  |  |  |

|----------|----------------------------|-------|-------|--|--|--|--|

| CP2[2:0] | 33kΩ                       | 27 kΩ | 22 kΩ |  |  |  |  |

| 000      | 0.69                       | 0.84  | 1.04  |  |  |  |  |

| 001      | 0.86                       | 1.06  | 1.30  |  |  |  |  |

| 010      | 1.04                       | 1.27  | 1.55  |  |  |  |  |

| 011      | 1.21                       | 1.48  | 1.81  |  |  |  |  |

| 100      | 1.38                       | 1.69  | 2.07  |  |  |  |  |

| 101      | 1.55                       | 1.90  | 2.33  |  |  |  |  |

| 110      | 1.73                       | 2.11  | 2.59  |  |  |  |  |

| 111      | 1.90                       | 2.32  | 2.85  |  |  |  |  |

#### FAST[12:0]: Sets the FAST counter value.

A decimal number from 1 to 8191 can be set. This counter value is used to set the time period during which the charge pump for the Fast Lockup mode is ON.

The charge pump for the Fast Lockup mode is turned OFF after the time period calculated by [this count value x phase detector frequency cycle]. 0 cannot be set.

#### Address 0x05

#### VTSEL[1:0]: Sets the noise detection level of noise squelch circuit.

#### Address 0x06

#### **OFST[17:0]**: Set the adjustable frequency offset in 2's complementary representation.

OFFSET register must be written at the speed calculated by "1/3.5\*RF Frequency/(INT+7)". If the writing speed is faster than this, the setting isn't valid.

This register is offset from carrier frequency.

After this register is accessed, NUM[17:0] and INT[14:0] are recalculated and their recalculated data are used in delta-sigma and N-divider. When this register is not used, this register must be written 00000 (hexadecimal).

When OFFSET register is used, set DITH=0(OFF).

#### Address 0x07

#### AGC\_KEEP: The function of AGC1/2 gain keeping

When the AGC function is active, the gain setting of AGC1/2 is kept during {AGC\_KEEP}=1. On the other hand, the gain setting of AGC1/2 is changed by IFIP signal during {AGC\_KEEP}=0.

0: the gain setting of AGC1/2 is changed by IFIP signal. (default)

1: the gain setting of AGC1/2 is kept.

AGCLVL H[2:0]: Setting the upper limit of AGC threshold level.

|          | 1. eegepp |          |               |

|----------|-----------|----------|---------------|

| AGCLVL_H | AGCLVL_H  | AGCLVL_H | upper limit   |

| [2]      | [1]       | [O]      |               |

| 0        | 0         | 0        | -5dB          |

| 0        | 0         | 1        | -4dB          |

| 0        | 1         | 0        | -3dB          |

| 0        | 1         | 1        | -2dB          |

| 1        | 0         | 0        | -1dB          |

| 1        | 0         | 1        | 0dB (default) |

| 1        | 1         | 0        | 1dB           |

| 1        | 1         | 1        | 2dB           |

AGCLVL\_L[2:0]: Setting the lower limit of AGC threshold level.

| ASSETT_E[E:0]: Setting the lower limit of ASS threshold level. |          |          |               |  |  |  |  |  |

|----------------------------------------------------------------|----------|----------|---------------|--|--|--|--|--|

| AGCLVL_L                                                       | AGCLVL_L | AGCLVL_L | lower limit   |  |  |  |  |  |

| [2]                                                            | [1]      | [0]      |               |  |  |  |  |  |

| 0                                                              | 0        | 0        | -8dB          |  |  |  |  |  |

| 0                                                              | 0        | 1        | -6dB          |  |  |  |  |  |

| 0                                                              | 1        | 0        | -4dB          |  |  |  |  |  |

| 0                                                              | 1        | 1        | -2dB          |  |  |  |  |  |

| 1                                                              | 0        | 0        | 0dB (default) |  |  |  |  |  |

| 1                                                              | 0        | 1        | 1dB           |  |  |  |  |  |

| 1                                                              | 1        | 0        | 2dB           |  |  |  |  |  |

| 1                                                              | 1        | 1        | 3dB           |  |  |  |  |  |

Note 1) When the AGC1/2 output level is bigger than the upper limit value, AGC1/2 gain is decreased. When the AGC1/2 output level is smaller than the lower limit value, AGC1/2 gain is increased. The upper/lower limit level is tunable based on default setting limit value.

Note 2) When AGC function is active ({AGC OFF}=0), AGC1/2 works as Note1...

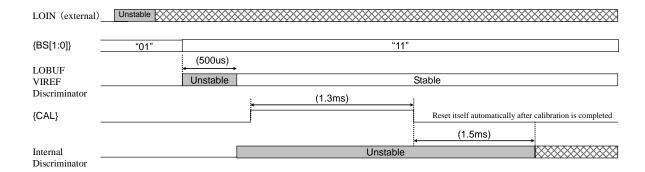

#### CAL: Discriminator circuit calibration start trigger Discriminator

0 : Invalid 1 : Start

Note ) : Calibration is performed synchronized with the rising edge of {CAL}.

After calibration completed, this register is set to "0" automatically. It takes 1.3ms before calibration is completed. Refer to "calibration procedure" for further information.

#### AGC\_FAST: AGC control switching

0 : AGC control is operated with AGC response time described in AGC\_TIME[1:0].

1 : The time constant of response time is changed by conditions that AGC1/AGC2 output level converges between the upper limit and lower limit(convergence) or not(attack/release). attack/release : AGC response time is the same as AGC\_TIME="00".

convergence : AGC response time is set with ACG\_TIME[1:0].

This setting provides the fast response time that can be followed the burst signal. (default)

#### AGC\_TIME[1:0]: AGC response time setting

This register set response time for AGC1 gain and AGC2 gain to change by 1step.

| AGC_TIME [1] | AGC_TIME | AGC response time [ms] |         |         |                     |         |         |  |  |

|--------------|----------|------------------------|---------|---------|---------------------|---------|---------|--|--|

|              |          | AGC1_STEP=0 setting    |         |         | AGC1_STEP=1 setting |         |         |  |  |

|              |          | State A                | State B | State C | State A             | State B | State C |  |  |

| 0            | 0        | (0.6)                  | (8.5)   | (8.5)   | (0.4)               | (4.4)   | (4.4)   |  |  |

| 0            | 1        | (67)                   | (95)    | (95)    | (34)                | (58)    | (58)    |  |  |

| 1            | 0        | (134)                  | (182)   | (182)   | (67)                | (111)   | (111)   |  |  |

| 1            | 1        | (267)                  | (355)   | (355)   | (134)               | (218)   | (218)   |  |  |

Note ): Values above indicate response time during AGC gain changes from maximum to minimum or from minimum to maximum.

State A: AGC1 output level is beyond the upper limit.

State B: AGC1 output level is within the upper limit and AGC2 output level is beyond the upper limit.

State C: AGC2 output level is under the lower limit.

#### AGC1\_STEP: AGC1 gain switching range setting

0: ±1dB

1: ±2dB (default)

### AGC\_OFF: AGC ON/OFF setting

0: ON (default)

1 : Off

BPF BW[2:0]: BPF band width setting

| Bit _Bit[2.0]. Bit band width setting |               |               |      |                 |                           |                              |  |  |  |

|---------------------------------------|---------------|---------------|------|-----------------|---------------------------|------------------------------|--|--|--|

| BPF_BW [2]                            | BPF_BW<br>[1] | BPF_BW<br>[0] | Name | 6dB attenuation | Attenuation band width    | Remarks                      |  |  |  |

| 1                                     | 0/1           | 0/1           | F0   | ±7.5kHz         | ±15kHz<br>(within 50dB)   |                              |  |  |  |

| 0                                     | 0             | 0             | F1   | ±6kHz           | ±12.5kHz<br>(within 50dB) |                              |  |  |  |

| 0                                     | 0             | 1             | F2   | ±4.5kHz         | ±11kHz<br>(within 50dB)   |                              |  |  |  |

| 0                                     | 1             | 0             | F3   | ±3kHz           | ±9kHz<br>(within 50dB)    |                              |  |  |  |

| 0                                     | 1             | 1             | F4   | ±2kHz           | ±7kHz<br>(within 50dB)    | 8dB attenuation at F4: ±2kHz |  |  |  |

LOFREQ[1:0]: Local frequency setting

| LOFREQ<br>[1] | LOFREQ<br>[0] | Local Frequency |

|---------------|---------------|-----------------|

| 0             | 0             | 45.9MHz         |

| 0             | 1             | 50.4MHz         |

| 1             | 0             | 57.6MHz         |

| 1             | 1             | 28.8MHz         |

#### Address 0x08

PGA0[2:0]: Gain setting of PGA0+2nd MIX

|         |         |         | •                      |

|---------|---------|---------|------------------------|

| PGA0[2] | PGA0[1] | PGA0[0] | PGA0+2nd MIX gain [dB] |

| 0       | 0       | 0       | (42)                   |

| 0       | 0       | 1       | (44)                   |

| 0       | 1       | 0       | (46)                   |

| 0       | 1       | 1       | (48) (default)         |

| 1       | 0       | 0       | (50)                   |

| 1       | 0       | 1       | (52)                   |

| 1       | 1       | 0       | (54)                   |

| 1       | 1       | 1       | (56)                   |

Note ) Test circuit is shown Figure 8 on page 15.

PGA0\_LG: When {PGA0\_LG}=1, PGA0+2nd MIX gain is fixed 28dB regardless of {PGA0[2:0]}.

0 : PGA0+2nd MIX gain is controlled by setting of {PGA0[2:0]} (default)

1 : PGA0+2nd MIX gain is 28dB fixed regardless of setting of {PGA0[2:0]}.

PGA2 G[4:0]: When AGC OFF="1", AGC2 gain setting is available.

| · · · · · · · · · · · · · · · · · · · |            |            |            |            |          |  |  |  |

|---------------------------------------|------------|------------|------------|------------|----------|--|--|--|

| PGA2_G[4]                             | PGA 2_G[3] | PGA 2_G[2] | PGA 2_G[1] | PGA 2_G[0] | Gain[dB] |  |  |  |

| 0                                     | 1          | 1          | 0          | 0          | 12       |  |  |  |

| 0                                     | 1          | 0          | 1          | 1          | 11       |  |  |  |

| 0                                     | 1          | 0          | 1          | 0          | 10       |  |  |  |

| 0                                     | 1          | 0          | 0          | 1          | 9        |  |  |  |

| 0                                     | 1          | 0          | 0          | 0          | 8        |  |  |  |

| 0                                     | 0          | 1          | 1          | 1          | 7        |  |  |  |

| 0                                     | 0          | 1          | 1          | 0          | 6        |  |  |  |

| 0                                     | 0          | 1          | 0          | 1          | 5        |  |  |  |

| 0                                     | 0          | 1          | 0          | 0          | 4        |  |  |  |

| 0                                     | 0          | 0          | 1          | 1          | 3        |  |  |  |

| 0                                     | 0          | 0          | 1          | 0          | 2        |  |  |  |

| 0                                     | 0          | 0          | 0          | 1          | 1        |  |  |  |

| 0                                     | 0          | 0          | 0          | 0          | 0        |  |  |  |

Note: Do not set the combination of the code which is not defined in the table given above.

PGA1\_G[5:0]: When AGC\_OFF="1", AGC1 gain setting is available.

|           | <i>G[5:0]</i> : wnen |           |           |                   |           |            |

|-----------|----------------------|-----------|-----------|-------------------|-----------|------------|

| PGA1_G[5] | PGA1_G[4]            | PGA1_G[3] | PGA1_G[2] | PGA1_G[1]         | PGA1_G[0] | Gain[dB]   |

| 0         | 1                    | 0         | 1         | 0                 | 1         | 21         |

| 0         | 1                    | 0         | 1         | 0                 | 0         | 20         |

| 0         | 1                    | 0         | 0         | 1                 | 1         | 19         |

| 0         | 1                    | 0         | 0         | 1                 | 0         | 18         |

| 0         | 1                    | 0         | 0         | 0                 | 1         | 17         |

| 0         | 1                    | 0         | 0         | 0                 | 0         | 16         |

| 0         | 0                    | 1         | 1         | 1                 | 1         | 15         |

| 0         | 0                    | 1         | 1         | 1                 | 0         | 14         |

| 0         | 0                    | 1         | 1         | 0                 | 1         | 13         |

| 0         | 0                    | 1         | 1         | 0                 | 0         | 12         |

| 0         | 0                    | 1         | 0         | 1                 | 1         | 11         |

| 0         | 0                    | 1         | 0         | 1                 | 0         | 10         |

| 0         | 0                    | 1         | 0         | 0                 | 1         | 9          |

| 0         | 0                    | 1         | 0         | 0                 | 0         | 8          |

| 0         | 0                    | 0         | 1         | 1                 | 1         | 7          |

| 0         | 0                    | 0         | 1         | 1                 | 0         | 6          |

| 0         | 0                    | 0         | 1         | 0                 | 1         | 5          |

| 0         | 0                    | 0         | 1         | 0                 | 0         | 4          |

| 0         | 0                    | 0         | 0         | 1                 | 1         | 3          |

| 0         | 0                    | 0         | 0         | 1                 | 0         | 2          |

| 0         | 0                    | 0         | 0         | 0                 | 1         | 1          |

| 0         | 0                    | 0         | 0         | 0                 | 0         | 0          |

| 1         | 1                    | 1         | 1         | 1                 | 1         | -1         |

| 1         | 1                    | 1         | 1         | 1                 | 0         | -2         |

| 1         | 1                    | 1         | 1         | 0                 | 1         | -3         |

| 1         | 1                    | 1         | 1         | 0                 | 0         | -4         |

| 1         | 1                    | 1         | 0         | 1                 | 1         | -5         |

| 1         | 1                    | 1         | 0         | 1                 | 0         | -6         |

| 1         | 1                    | 1         | 0         | 0                 | 1         | -7         |

| 1         | 1                    | 1         | 0         | 0                 | 0         | -8         |

| 1         | 1                    | 0         | 1         | 1                 | 1         | -9         |

| 1         | 1                    | 0         | 1         | 1                 | 0         | -10        |

| 1         | 1                    | 0         | 1         | 0                 | 1         | -11        |

| 1         | 1                    | 0         | 1         | 0                 | 0         | -12        |

| 1         | 1                    | 0         | 0         | 1                 | 1         | -13        |

| 1         | 1                    | 0         | 0         | 1                 | 0         | -14        |

| 1         | 1                    | 0         | 0         | 0                 | 1         | -15        |

| 1         | 1                    | 0         | 0         | 0                 | 0         | -16        |

| 1         | 0                    | 1         | 1         | 1                 | 0         | -17        |

| 1         | 0                    | 1         | 1         | 0                 | 1         | -18<br>-19 |

| Note: F   |                      |           | <u>'</u>  | not defined in th | <u> </u>  | -18        |

Note: Do not set the combination of the code which is not defined in the table given above.

IFOG[2:0]: IFBUF Gain setting.

| IFOG<br>[2] | IFOG<br>[1] | IFOG<br>[0] | IFBUF Gain[dB] |

|-------------|-------------|-------------|----------------|

| 0           | 0           | 0           | 0              |

| 0           | 0           | 1           | 3 (default)    |

| 0           | 1           | 0           | 6              |

| 0           | 1           | 1           | 9              |

| 1           | 0           | 0           | 12             |

| 1           | 0           | 1           | 15             |

#### Address 0x09

#### **Software-reset**

When data 0x09:10101010 is written to the SRST[7:0] register, software reset is performed.

#### Address 0x0A

PDN,BS[2:0]: 2nd IF Block Operation mode setting

|     | r DIN,D   | <u> </u>  | ZIIU II   | Block Operation           |          | ie semnić           | 1                   |                                    |           |                   |                             |

|-----|-----------|-----------|-----------|---------------------------|----------|---------------------|---------------------|------------------------------------|-----------|-------------------|-----------------------------|

| PDN | BS<br>[2] | BS<br>[1] | BS<br>[0] | Mode name                 | LDO<br>D | LDOA,<br>AGNDI<br>N | LOBUF<br>,<br>VIREF | 2nd MIX<br>~SMF,<br>DIV,<br>AGCCNT | IFBU<br>F | LIMITE<br>R, RSSI | DISCRI,<br>Noise<br>Squelch |

| 0   | -         | -         | -         | Mode0<br>(Power<br>Down0) | OFF      | OFF                 | OFF                 | OFF                                | OFF       | OFF               | OFF                         |

| 1   | 0         | 0         | 1         | Mode1<br>(Note 1)         | ON       | OFF                 | OFF                 | OFF                                | OFF       | OFF               | OFF                         |

| 1   | 0         | 1         | 0         | Mode2<br>(Initial value)  | ON       | ON                  | OFF                 | OFF                                | OFF       | OFF               | OFF                         |

| 1   | 0         | 1         | 1         | Mode3                     | ON       | ON                  | ON                  | OFF                                | OFF       | OFF               | OFF                         |

| 1   | 1         | 0         | 0         | Mode4                     | ON       | ON                  | ON                  | ON                                 | ON        | OFF               | OFF                         |

| 1   | 1         | 0         | 1         | Mode5                     | ON       | ON                  | ON                  | ON                                 | ON        | ON                | OFF                         |

| 1   | 1         | 1         | 0         | Mode6                     | ON       | ON                  | ON                  | ON                                 | OFF       | ON                | ON                          |

| 1   | 1         | 1         | 1         | Mode7                     | ON       | ON                  | ON                  | ON                                 | ON        | ON                | ON                          |

Note 1): Do not use Mode1.

Note 2): Do no set the combination of the code which is not defined in the table given above.

#### DISLPF G[2:0]: Setting of the demodulation output level

| = 1 1/2 - 1 1 |              |              |                                                          |

|---------------|--------------|--------------|----------------------------------------------------------|

| DISLPF_G[2]   | DISLPF_G [1] | DISLPF_G [0] | Demodulation output level when ±1.5kHz dev. signal input |

| 0             | 0            | 1            | 100mVrms                                                 |

| 0             | 1            | 0            | 200mVrms                                                 |

| 0             | 1            | 1            | 300mVrms                                                 |

| 1             | 0            | 1            | 50mVrms                                                  |

| 1             | 1            | 0            | 100mVrms                                                 |

| 1             | 1            | 1            | 150mVrms                                                 |

Note ) The demodulation output level (±1.5kHz dev. signal input, AUDIOOUT pin output) can be set to 50mVrms typ. to 300mVrms typ. by setting of {DISLPF\_G[2:0]}.

Note ) Do no set the combination of the code which is not defined in the table given above.

#### AGC\_KEEP\_SEL: Select AGC function of gain keeping

This register set the control way of the function of gain keeping.

0 : Control by the register {AGC\_KEEP} setting (default)

1 : Control by the pin of AGC\_KEEP

#### SDATAOUT\_OE: Select output signal of DETO/SDATAOUT pin

The signal of DETO or SDATAOUT can be output from DETO/SDATAOUT pin.

0 : DETO signal output (default)1 : SDATAOUT signal output

### FMIX IP3: NF/IIP3 priority select of 1st Mixer

IIP3 performance of 1st Mixer is improved by setting  $\{FMIX\_IP3\}=1$  without more supply current. Then Current Adjustment Resistor (BIAS1/2) must be used <  $47k\Omega$ . If NF performance is more important than IIP3, setting  $\{FMIX\_IP3\}=0$ .

0: NF performance is preference (default)

1: IIP3 performance improvement

#### FMIX\_HV: High IIP3 mode of 1st Mixer

IIP3 performance of 1st Mixer is improved by adjustment of BIAS1/2 resistance and setting {FMIX HV}="1". When FMIX HV="1" setting, MIXVDD must be set more than 4.5V.

0 : BIAS1/2  $\geq$  39k $\Omega$  (default) 1 : 18k $\Omega$   $\leq$  BIAS1/2 < 39k $\Omega$

#### PDTRI\_N: Tripler circuit On/Off

REFIN signal can be input from LO2NDIN pin by setting tripler circuit off. Then REFIN input is one third of the 2nd LO input frequency.

0 : Off (default)

1: On

### PDSYNTH\_N: SYNTH On/Off

0 : Off (default)

1: On

#### PDADC N: ADC On/Off

0 : Off (default)

1: On

#### PDFSTMIX\_N: 1st MIXER On/Off

0: Off (defaut)

1: On

#### **BSSEL FMIX**: Bias resistance select

0 : BIAS2 pin is enable (default)

1: BIAS1 pin is enable

#### Address Ox0B

R\_AGC1\_G[5:0]: Read the gain setting of AGC1 when {AGC\_OFF}=0 R AGC2 G[4:0]: Read the gain setting of AGC2 when {AGC OFF}=0

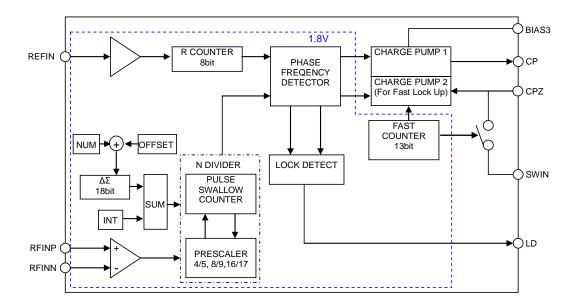

# **Block Diagram (PLL SYNTH)**

The AK2400 is a Delta-Sigma Fractional-N PLL (Phase Locked Loop) frequency synthesizer with a frequency switching function, covering a wide range of frequencies from 10 to 1000MHz. This product consists of an 18-bit Delta-Sigma modulator, a low-noise phase frequency comparator, a highly accurate charge pump, a reference divider, dual-module prescaler (P/P+1) and frequency offset adjustable circuits. An excellent PLL can be achieved by combining this synthesizer with the external loop filter and VCO (Voltage Controlled Oscillator). The operating supply voltage is from 2.7 to 5.5V; and the charge pump and serial interface can be driven by individual supply voltages.

Figure 9 Block Diagram (PLL SYNTH)

### Lock Detect function (PLL SYNTH)

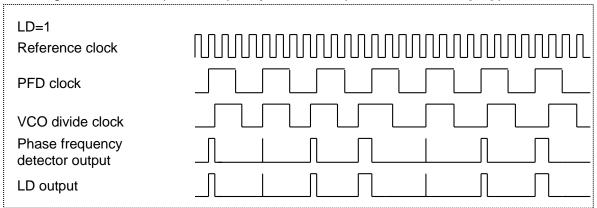

In AK2400, "lock detect" output can be selected by D[11] = {LD} in <Address3>. When {LD} is set to "1", the phase frequency detector output provides a phase detection status as an analog level (comparison result). This is called "Analog Lock Detect". When {LD} is set to "0", the lock detect signal outputs according to the on-chip logic. This is called "Digital Lock Detect".

#### **Analog Lock Detect**

In analog lock detect, the phase frequency detector output comes from the [LD] pin.

Figure 10 Analog Lock Detect

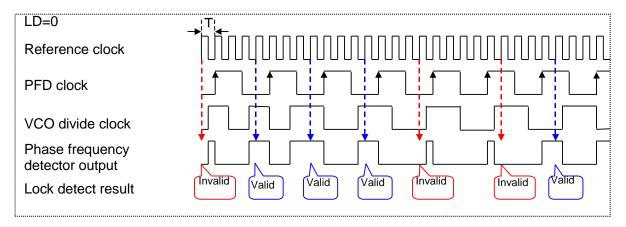

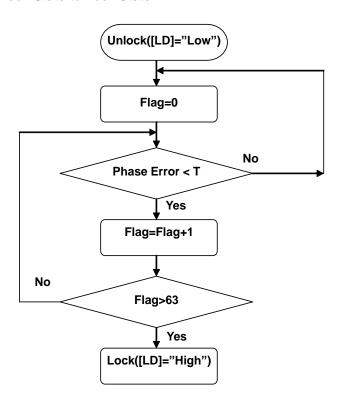

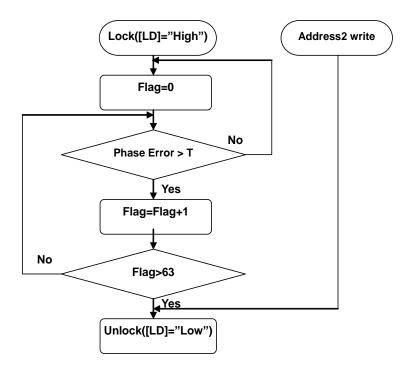

#### **Digital Lock Detect**

In the digital lock detect, the LD pin outputs "Low" every time when the frequency is set. And the LD pin outputs is "High" (which means the locked state) when a phase error smaller than T is detected for 63 times consecutively. If the phase error is larger than T is detected for 63 times consecutively when the LD pin outputs "High", the LD pin outputs "Low" (which means the unlocked state).

The accuracy of the phase detect is set by LDCKSEL[1:0].

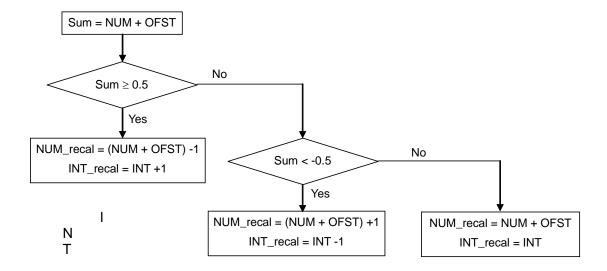

"00": 1 cycle of the REFIN clock (This cannot be used for the reference dividing ratio  $\leq$  3.) "01": 2 cycle of the REFIN clock (This cannot be used for the reference dividing ratio  $\leq$  5.) "10": 3 cycle of the REFIN clock (This cannot be used for the reference dividing ratio  $\leq$  6.)